#### Servo Controller

#### Description

The Hitachi HD49741NT/HD49733NT servo LSI for video tape recorders features an on-chip digital servo function for the drum motor and capstan motor, as well as an analog amplifier system, for wide-ranging applications on a variety of video tape recorder models. Available in a 56-pin shrink DIP package, HD49741NT/HD49733NT provides serial control connections with the system controller (microcomputer). This provides full servo LSI functions and means fewer peripheral components and connections are required.

#### **Features**

- · Conforms to both PAL and NTSC standards.

- In conjunction with set function, mask ROM options allow setting of CFG (capstan frequency), DFG (drum frequency, search speed, etc.

- All VISS (VHS index search system) included on chip, with rewriting also possible.

- Search and output also available for VASS (VHS address search system), so operation in combination with microcomputer provides a full range of functions.

- CMOS analog technology provides on-chip CFG, DFG, PG (pulse generator), and CTLP (control pulse) amplifier, as well as adder amplifier loop f-characteristics, and analog switching for gain correction.

- Serial control used by microcomputer interface, so the system requires fewer connections.

### **Functional Description**

#### DAC output using switched capacitor

Drum, capstan PD (phase detect), and FV (frequency voltage) conversion output is performed using switched capacitor technology for output of DC voltage. This means that, unlike conventional PWM output, a carrier elimination filter is not required. See Appendix B on SCF for further details.

## 70 different search speed variations on a single chip

Search speed is set using the mask ROM options. 14 speeds each for the SP, LP and EP modes in a NTSC system, as well as 14 modes each for the LP and LP modes in a PAL system are provided for a total of possible search speed settings. For further details, see serial control codes in On-chip Functions, and Mask ROM Options.

#### Six head angle settings

The head switch position is determined according to the PG mono-multi from the drum PG pulse. However, when the video head and audio head positions are different (when the video head is 4-head orthogonal/4-head double azimuth, the audio head is normally at a different position), a SW30 signal position (which indicates a fixed angle head switch position) is required for the head switch position created by the PG mono-multi. HD49741NT/HD49733NT allows six angle setting options for SW30 signals, for audio, video, and extra (extra head can be used for moving head, flying erase, etc.) heads. For further details, see serial control codes in On-chip Functions, Mask ROMs, and Timing Chart.

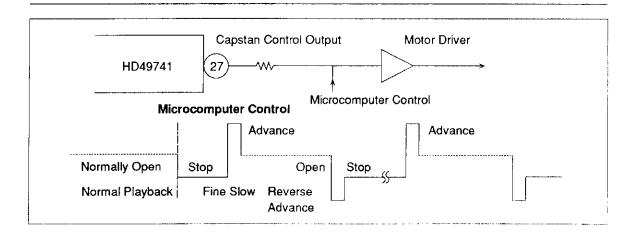

#### 10 fine slow speed settings

Fine slow is made possible by intermittent tape transport, which is performed as illustrated below.

During fine slow, the speed of the capstan is controlled during the period from the point following the advance up to reverse advance in order to eliminate noise and to correct picture distortion. HD49741NT/HD49733NT allows serial control to be used to set this speed.

## 7-bit serial data and CR mono-multi setting of X-value correction

X-value correction (control pulse position correction) can be performed using serial control (Pin 5 CTL MM) or by altering the CR mono-multi time constant. For details, see Pin Functions and On-chip Functions.

#### 7-bit serial data setting of tracking

Tracking can be controlled using serial control. For details, see On-chip Functions.

## Supplementary V-pulse position delay (position) and shift settable using serial data

The delay time from the V-head switch edge to the supplementary V-pulse differs according to the special playback mode, which uses SW30 as a reference. HD49741NT/HD49733NT allows setting of this delay time (VP position) with the input of serial data. Serial data input can also be used to control the shift required during fine slow between the supplementary V-pulse position during acceleration (frame-by-frame) and the V-pulse position in the stop state. For details, see On-chip Functions.

#### Selection between f<sub>sc</sub> and 3f<sub>sc</sub> using serial data

The master clock of HD49741NT/HD49733NT is capable of using either  $f_{sc}$  or  $3f_{sc}$ . In the case of an  $f_{sc}$  master clock, crosstalk tends to be generated because  $f_{sc}$  enters the luminance FM band, while  $3f_{sc}$  suppresses crosstalk generation. For details, see On-chip Functions.

# Cross-over color distortion minimized by $f_H$ correction using H-sync discrete integration

The drum speed system requires  $f_H$  correction to correct the H-cycle changes that occur in the special playback mode. HD49741NT/HD49733NT includes an  $f_H$  correction function that constantly monitors and corrects the H-sync cycle, so correction during startup of special playback minimizes cross-over color distortion and horizontal distortion. For details, see On-chip Functions.

## Noise and no-H sync detection output for screen blackout

HD49741NT/HD49733NT counts the number of pulses in the H-sync frame, as well as the number of noise pulses within 1H period to provide output when the electric field strength is approximately below 4.0 to 4.5dBµ. This output is produced at the mode pin, and can be used for screen black-out when receiving channels for which there is no broadcast, etc. For details, see On-chip Functions.

#### Frame servo function

With VHS, recording and playback are performed with the CH1 head in the odd mode, and the CH2 in the even mode, though some manufacturers have

chosen to ignore this convention recently. HD49741NT/HD49733NT performs recording while precisely differentiating between these two modes, so the odd-even relationship is maintained for assembled recordings. During playback, beautiful assemblies are possible because the misaligned V signals instantaneously generated during playback are eliminated.

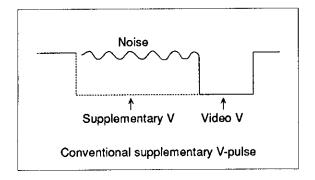

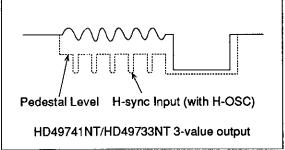

## Supplementary V-pulse settable to H-OSC 3-value output or 2-pin output (HD49741NT)

Supplementary V-pulse is traditionally added immediately before the video V-pulse to protect against malfunction caused by noise. This method, however, generates mis-aligned V signals during special playback, can causes the playback screen to drop. HD49741NT/HD49733NT provides the V-pulse correction illustrated below.

This provides a choice of supplementary V-pulse signals: 3-value output (Pin 48) with sync level, pedestal level, and unsupplemented level; and 2-value output (Pin 48 and Pin 49). Note that the 2-pin output is available with HD49741NT only. For details, see On-chip Functions.

## 3 head switch outputs: Video-FF, audio-FF, extra-FF

Besides video and audio-FF, HD49741NT/ HD49733NT includes extra-FF output designed for moving head and flying erase. FF angles are set using the mask ROM options for each head (note there is no extra head FF with HD49733NT). For details on head angle and head switching, see serial control codes in On-chip Functions, and Mask ROM Options.

#### On-chip V-sync separator circuit HD49741NT/HD49733NT performs V-sync

separation up/down counting the H-sync pulse input at the CMP-SYNC pin (Pin 50), so an external low-pass filter is not required.

## Analog signal input received by Schmitt circuit for rejection of other digital noise

HD49741NT/HD49733NT features on-chip DFG, CFG, PG, and DTLP input amplifiers with a Schmitt circuit for the elimination of small noise. Also, input of a pulse is followed by a preset period for digital processing, during which further input is cutoff, protecting against the invasion of noise between signals.

#### **External synchronization input**

With VTRs using frame memory, it is necessary to synchronize the reference frame signal of the frame memory controller (which is a signal equivalent to that of REF-30 of the servo IC) with REF-30 of the servo IC. HD49741NT/HD49733NT supports this type of synchronization. REF-30 (Pin 44) should be used when synchronization of the frame memory controller is necessary. Note that the pins used with HD49741NT are different from those used with HD49733NT. For details, see On-chip Functions.

## CFG and CTLP output for SP/LP/EP discrimination

HD49741NT/HD49733NT does not include an onchip SP/LP/EP discrimination function, but outputs CFG and CTLP so the microcomputer can perform such discrimination. Even during search operations, output signals are generated by counting down the CFG and CTLP pulses in accordance with the search speed, resulting in a constant pulse cycle. For details, see On-chip Functions.

#### Non-linear PD output

With the drum and capstan PD function, 2-level detection output is required, with a large output gain for large errors, and small output during normal conditions. This is to allow both quick phase synchronization when a phase detection error occurs, and stability during normal conditions. HD49741NT/HD49733NT include these detection characteristics on-chip, so there is no need to attach the external non-linear circuitry required in the past.

## VISS discrimination capability even at more than 200X speed search

HD49741NT/HD49733NT performs VISS discrimination by pulse counting CTLP duty. A high-speed count clock allows detection of the VISS signal even in a 200X speed search mode.

## On-chip waveform blunting, CTL, duty rewriting

For VISS rewriting, it is necessary to blunt the CTLP rise in order to protect against damage to the previously written CTLP signal. HD49741NT/HD49733NT apply CMOS analog technology to create an on-chip blunting circuit, so fewer external

VISS functions are required.

## On-chip automatic writing and discrimination of VISS code

VISS writing is performed automatically under serial control, with the blunting circuit operational during playback but not during recording. During playback, Pin 40 becomes LOW to indicate that VISS is detected.

## CTLP amplifier with high f-characteristics, high gain, and fast rise at power ON

There is generally a problem with the rise speed of the CTLP amplifier at power ON. Since charge up time is required for external capacitance, however, the rise speed problem has generally been a hard to solve. HD49741NT/HD49733NT adopt a new type of circuitry is configured to eliminate the need for charge up, providing a quick-rise CTLP amplifier.

#### CTLP Schmitt input with three threshold levels

The Schmitt circuit of the CTLP amplifier allows stable operations over three switchable operation levels.

3-level threshold voltage switching performed automatically in accordance with SP, LP, EP, and search. Threshold level selection is performed automatically when the playback mode is set.

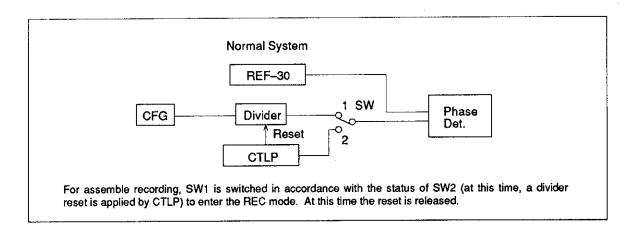

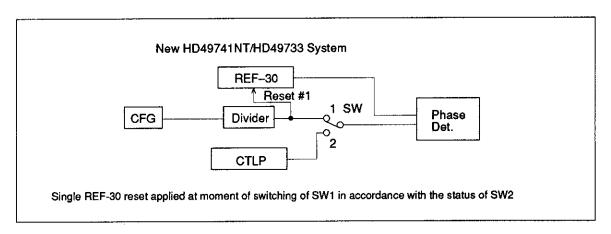

#### High-precision assemble

Assemble recording is performed using capstan phase control. Normally, the system is configured as illustrated below, but the improved precision of HD49741NT/HD49733NT allows use of a new system.

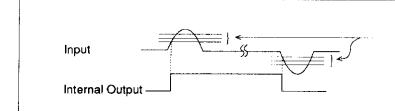

#### Fine slow CTLP Schmitt retrigger function

During fine slow, there are cases in the forward mode in which negative CTLP does not follow positive CTLP. To counteract this, HD49741NT/ HD49733NT generate the subsequent CTLP

signal automatically if the following pulse is not detected for approximately 10ms after the leading CTLP is entered.

# Power ON reset without CTL head error current during full-rotating, half-rotating power ON

There are cases in which the tape is in its rotating status when the power of the VCR is OFF. HD49741NT/HD49733NT resets the CTL write circuit at power ON, no matter what the tape status, to protect against writing of the CTLP pulse. For details, see Pin Functions.

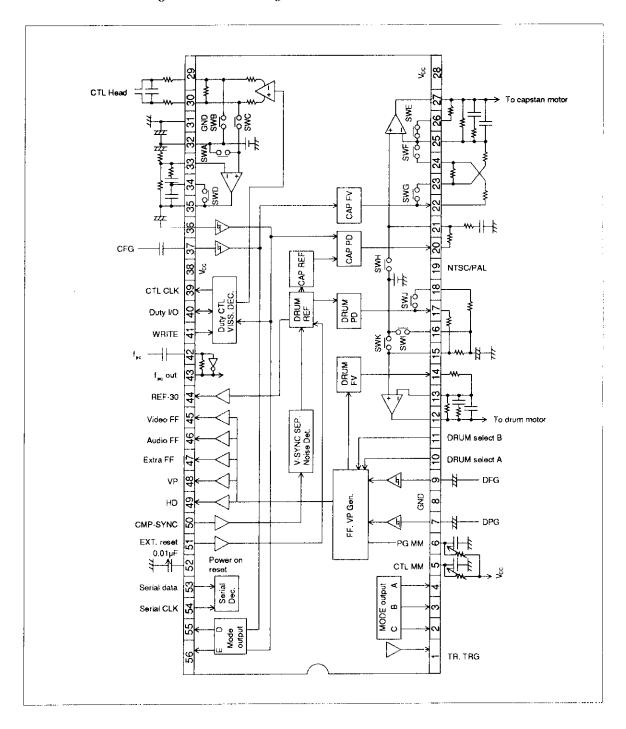

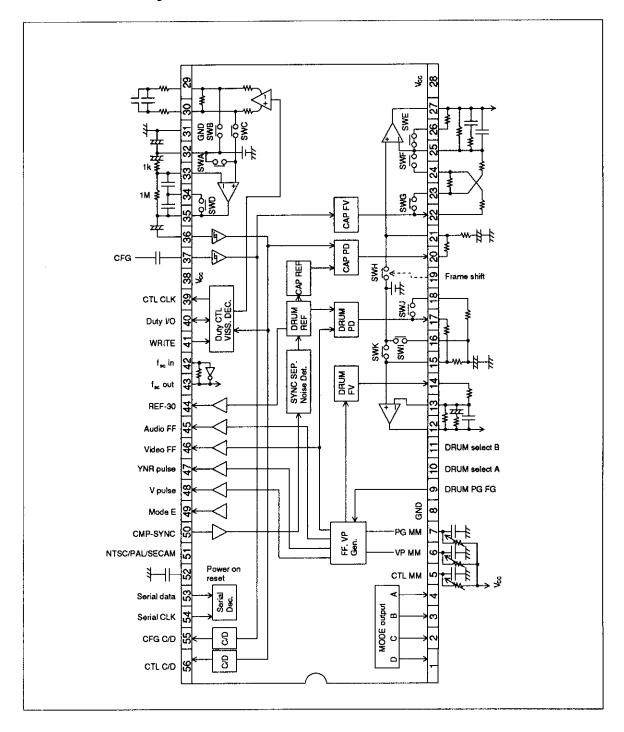

### **Block Diagram**

### **HD49741NT Block Diagram and Pin Arrangement**

### **HD49733NT Block Diagram and Pin Arrangement**

## **Pin Functions**

### **HD49741NT Pin Functions**

| Pin<br>No. | Pin Name                             | Fund                        | ctio   | n            |    |     |                              |         |                          | I/O Format |

|------------|--------------------------------------|-----------------------------|--------|--------------|----|-----|------------------------------|---------|--------------------------|------------|

| 1          | TRACKING<br>TRIGGER                  |                             |        |              |    |     |                              |         | •                        |            |

| 2          | MODE OUTPUT                          | bit 5                       | 4      | 2            | 1  | 0   | Α                            | В       | С                        |            |

| 3          | reference                            | 0                           | 0      | 1            | 1  | 1   | SP                           | SP      | LP                       |            |

| 4          |                                      | 0                           | 1      | 1            | 1  | 1   | SP                           | EΡ      | LP                       |            |

|            | 1 0 1 1 1 CTL DELAY H-OSC Noise Det. |                             |        |              |    |     |                              |         | Noise Det.               |            |

|            |                                      | 1                           | 1      | 1            | 1  | 1   | CAP PD                       | DRUM FG | DRUM PG                  |            |

|            |                                      | See<br>Refe<br>Refe<br>Refe | r to i | Time<br>H-OS |    |     |                              |         |                          |            |

| 5          | CTL DELAY<br>MM                      |                             |        |              |    |     | 40ms See Ti<br>harge pulse = |         | Compa- ↑ V <sub>CC</sub> |            |

| 6          | PG MM                                | Time<br>See I<br>Non-       | Head   | d SW         | ΪŢ | imi | 60° DEG<br>ng                |         | V <sub>CC</sub> / 1      |            |

| Pin<br>No.                       | Pin Name           | Function                                                  |        |                                              |                                        |                | I/O Format                                                                                            |

|----------------------------------|--------------------|-----------------------------------------------------------|--------|----------------------------------------------|----------------------------------------|----------------|-------------------------------------------------------------------------------------------------------|

| 7                                | DRUM PG IN         | Approximately 2<br>Schmitt input/in<br>See Head SW        | ternai | +V <sub>TP</sub><br>-V <sub>TH</sub><br>Bias | <b>←</b> ≪ <u></u>                     |                |                                                                                                       |

| 9                                | DRUM FG IN         | Approximately 2<br>Schmitt input/in<br>See Head SW 1      | ternai | +V <sub>TH</sub><br>∕- Bias                  |                                        |                |                                                                                                       |

| 10<br>11                         | DRUM select A      | 3-value input<br>Open = "M"                               | ВА     | ≅ 30kΩ<br>* TEST is u <u>se</u> d for        |                                        |                |                                                                                                       |

|                                  |                    | (1.9V to 3.1V)<br>See Head<br>SW Timing                   | Н      | DA4-@                                        | checking SP in the                     |                |                                                                                                       |

|                                  |                    | Different from selection                                  | М      | DA4-3                                        | azimuth head set.<br>When this mode is |                |                                                                                                       |

|                                  |                    | format for<br>HD49733.                                    | L      | DA4 ①<br>TEST*                               | DA4-②<br>TEST*                         | DA4-③<br>TEST* | specified,<br>HD49741NT/<br>HD49733NT                                                                 |

|                                  |                    |                                                           |        |                                              |                                        |                | recognizes SP mode tape as LP mode tape, and inverts the head selection switch to run in the SP mode. |

| 21<br>23<br>24<br>25<br>26<br>27 | CAPSTAN<br>MIX Amp | Open gain  No oscillation during all feed  Output D range | 8      | · Iz                                         |                                        |                |                                                                                                       |

| 12<br>13<br>15<br>16<br>18       | DRUM<br>MIX Amp    | O to 5V (no loa Output impeda                             |        | 2kΩ max.                                     |                                        |                |                                                                                                       |

| Pin<br>No.           | Pin Name    | Function                                                                                              | Function                                                          |                    |                  |    |                                              |                              |  |  |  |  |

|----------------------|-------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------|------------------|----|----------------------------------------------|------------------------------|--|--|--|--|

| 14<br>22             | Drum FV out | Switched capacitor Output D range = 0. Input impedance =                                              | 5V n                                                              | nax. to 4.3V i     | nin.             |    |                                              | +                            |  |  |  |  |

| 17                   | Drum PD out | Switched capacitor Output D range = 0.                                                                |                                                                   |                    | min.             |    |                                              |                              |  |  |  |  |

| 20                   | CAP PD out  |                                                                                                       | Output D range = 0.5V max. to 4.3V min. Input impedance = 2Ω max. |                    |                  |    |                                              |                              |  |  |  |  |

| 19                   | NTSC/PAL    | 2-value input<br>open = "H"                                                                           |                                                                   | ·                  | Н                |    | NTSC                                         | ≅ 30kΩ ≩                     |  |  |  |  |

|                      |             | open = 11                                                                                             | L PAL                                                             |                    |                  |    |                                              |                              |  |  |  |  |

| 29                   | CTL Head ⊝  | I/O control head pin                                                                                  | O control head pin                                                |                    |                  |    |                                              |                              |  |  |  |  |

| 30                   | CTL Head ⊕  |                                                                                                       |                                                                   |                    |                  |    |                                              |                              |  |  |  |  |

| 32<br>33<br>34<br>35 | CTLP Amp    | Output D range 0 t                                                                                    | 80dB 10kHz                                                        |                    |                  |    |                                              |                              |  |  |  |  |

| 36                   | CTLP IN     | Schmitt input V <sub>TH</sub> 3-<br>switching<br>Approximately 2.5V<br>See CTL Schmitt V <sub>T</sub> | inter                                                             |                    | Д                | Ĵ  | +V <sub>ТН</sub><br>Віаѕ<br>–V <sub>ТН</sub> |                              |  |  |  |  |

| 37                   | CFG IN      | Same as DFG IN.                                                                                       |                                                                   |                    |                  |    |                                              |                              |  |  |  |  |

| 39                   | CTL CLK     | 2-value output, pull<br>See VISS, VASS                                                                | 2-value output, pull up<br>See VISS, VASS                         |                    |                  |    |                                              |                              |  |  |  |  |

| 40                   | Duty I/O    | 2-value input/output<br>pull up<br>See VISS, VASS                                                     | ,                                                                 | Input<br>Duty Mode | Output<br>VISS n |    | ode                                          | √V <sub>CC</sub><br>≅ ≅ 10kΩ |  |  |  |  |

|                      |             | 366 A100, A400                                                                                        | Н                                                                 | Duty = "0"         | VISS r           | 10 | n-detect                                     |                              |  |  |  |  |

|                      |             |                                                                                                       | L                                                                 | Duty = "1"         | VISS o           | le | tect (latch)                                 | 777                          |  |  |  |  |

| Pin<br>No.     | Pin Name                                   | Function                                                                                                                                                             |                                         |                    | I/O Format             |

|----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|------------------------|

| 41             | WRITE                                      | 2-value output, pull up<br>See VISS, VASS                                                                                                                            | -                                       | PB CTL, rewrite    | ≅ 10kΩ ¥  ←            |

| 42<br>43       | f <sub>sc</sub> in<br>3f <sub>sc</sub> out | Input sensitivity 150m Vpp<br>350m Vpp<br>With oscillator function<br>See f <sub>sc</sub> Input Circuit.<br>For f <sub>sc</sub> /3f <sub>sc</sub> switching, see Ser | min. (3                                 | if <sub>sc</sub> ) | ≸ ≅ 10kΩ               |

| 44<br>45<br>46 | REF 30<br>VFF<br>AFF                       | See Time Chart.  See Head SW Timing.  See Head SW Timing.                                                                                                            |                                         |                    | _>>                    |

| 47<br>49       | EFF<br>HD                                  | See Head SW Timing. See V-pulse Timing.                                                                                                                              |                                         |                    |                        |

| 48             | V-pulse (VP)                               | See V-pulse.                                                                                                                                                         |                                         |                    | = 20kΩ<br>= 20kΩ       |

| 50             | CMP SYNC                                   | 2-value input • Digital level capacitive co                                                                                                                          |                                         |                    | Input impedance ≅ 28kΩ |

| 51             | Ext. Reset                                 | 3-value input Open = "M" See External Synchronization                                                                                                                | ← → → → → → → → → → → → → → → → → → → → |                    |                        |

| Pin<br>No. | Pin Name        | Function                                                                                                                                                                                                                                                                                                              | I/O Format                                                                                                             |         |          |  |  |  |  |  |  |  |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------|----------|--|--|--|--|--|--|--|--|

| 52         | Power ON Reset  | flow to CTL head.                                                                                                                                                                                                                                                                                                     | At power ON, reset performed to current does not flow to CTL head. Be sure to include 0.01μF between this pin and GND. |         |          |  |  |  |  |  |  |  |  |

| 53         | Serial Data     | 2-value input (Schr                                                                                                                                                                                                                                                                                                   | mitt)                                                                                                                  |         | ↑ Vcc    |  |  |  |  |  |  |  |  |

| 54         | Serial CLK      | See Serial Input.                                                                                                                                                                                                                                                                                                     |                                                                                                                        |         | € ≅ 10kΩ |  |  |  |  |  |  |  |  |

| 55         | Mode            | bit 3 2 1 0                                                                                                                                                                                                                                                                                                           | D                                                                                                                      |         |          |  |  |  |  |  |  |  |  |

| 56         | output          | 0 1 1 1                                                                                                                                                                                                                                                                                                               | CFG C/D                                                                                                                | CTL C/D |          |  |  |  |  |  |  |  |  |

|            |                 | 1 1 1 1                                                                                                                                                                                                                                                                                                               |                                                                                                                        |         |          |  |  |  |  |  |  |  |  |

|            |                 | CFG C/D: CFG counted down according to search speed and then is output.  CTL C/D: CTL counted down according to search speed and then is output.  CFG 30: During REC, CFG countdown 30Hz  (25Hz for PAL), which indicates capstan phase comparison signal is output  See 4. On-chip Functions, and Serial Data Table. |                                                                                                                        |         |          |  |  |  |  |  |  |  |  |

| 8<br>31    | GND             | Ground                                                                                                                                                                                                                                                                                                                |                                                                                                                        |         |          |  |  |  |  |  |  |  |  |

| 28<br>38   | V <sub>CC</sub> | Connected to V <sub>CC</sub>                                                                                                                                                                                                                                                                                          | supply                                                                                                                 |         |          |  |  |  |  |  |  |  |  |

### **HD49733NT Pin Functions**

| Pin<br>No.       | Pin Name        | Function                                           | I/O Format |                                                                                                                                      |                                                            |                    |                                                      |

|------------------|-----------------|----------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|------------------------------------------------------|

| 1<br>2<br>3<br>4 | Mode Output     | See 4. On-chip                                     | Func       | table.                                                                                                                               | For SP, and SP mode output, high impedance and HIGH level. |                    |                                                      |

| 5                | CTL DELAY<br>MM | Time constant:<br>See Time Char<br>Retriggerable ( | t          |                                                                                                                                      | Compa-↑Vcc                                                 |                    |                                                      |

| 6                | VP MM           | Time constant:<br>Non-retriggeral                  |            | .6ms                                                                                                                                 |                                                            |                    | V <sub>CC</sub>                                      |

| 7                | PG MM           | Time ∞nstant:<br>Non-retriggerat                   | -          |                                                                                                                                      | 2 777 777                                                  |                    |                                                      |

| 9                | DRUM PFG IN     | 3-value input, c                                   | pen =      | "M"                                                                                                                                  |                                                            | -                  | $\leftarrow$                                         |

| 10<br>11         | DRUM select A   | 3-value input<br>Open = "M"<br>(1.9V to 3.1V)      | BA         | Н                                                                                                                                    | М                                                          | L                  |                                                      |

|                  |                 | Different from selection format for                | н          | DA4 ①                                                                                                                                | 2Head                                                      | 4Head<br>HiFi      | <u>≅</u> 30kΩ                                        |

|                  |                 | HD49741.                                           | М          | DA4 ②                                                                                                                                | 4Head                                                      | 4Head<br>HiFi      | * TEST is used for checking SP in the                |

|                  |                 |                                                    | L          | DA4 ②<br>TEST                                                                                                                        | 4Head<br>TEST                                              | 4Head<br>HiFi TEST | case of a double azimuth head set. When this mode is |

|                  |                 |                                                    |            | specified, HD49741NT/ HD49733NT recognize SP mode tape as LP mode tape, and inverts the head selection switch to run in the SP mode. |                                                            |                    |                                                      |

| Pin<br>No.                       | Pin Name               | Function                                                                                 |                                                                                                                        |           |                       | I/O Format          |  |  |  |  |  |

|----------------------------------|------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|---------------------|--|--|--|--|--|

| 21<br>23<br>24<br>25<br>26<br>27 | CAPSTAN<br>Mix Amp     | Open gain     No oscillation during all feedbac     Output D range     0 to 5V (no load) | k                                                                                                                      | 111111.   | 1kHz<br>0dB<br>nin.   |                     |  |  |  |  |  |

| 12<br>13<br>15<br>16<br>18       | DRUM<br>Mix Amp        | , , ,                                                                                    | • Output impedance = $2k\Omega$ max.                                                                                   |           |                       |                     |  |  |  |  |  |

| 14<br>22                         | DRUM FV out CAP FV out | Output D range = 0                                                                       | Switched capacitor DA output Output D range = 0.5V max, to 4.3V min. Input impedance = $100\Omega$ max.                |           |                       |                     |  |  |  |  |  |

| 17<br>20                         | DRUM PD out            | Output D range = 0                                                                       | Switched capacitor DA output Output D range = $0.5V$ max. to $4.3V$ min. Input impedance = $2\Omega$ max.              |           |                       |                     |  |  |  |  |  |

| 19                               | FRAME SHIFT            | • Frame shift                                                                            |                                                                                                                        | Out       | In                    | ←≪                  |  |  |  |  |  |

|                                  | (CAP PD Fix)           | PD fix<br>Tape speed                                                                     | Н                                                                                                                      |           | FRAME SHIFT           | <b>←</b> ∞ <b>→</b> |  |  |  |  |  |

|                                  |                        | 5% down During normal                                                                    | М                                                                                                                      | Loop on   | Loop on               | ↑ V <sub>cc</sub>   |  |  |  |  |  |

|                                  |                        | mode only                                                                                | L                                                                                                                      | PD Fix    | PD Fix                |                     |  |  |  |  |  |

| 29                               | CTL Head               | I/O control head pin                                                                     |                                                                                                                        |           |                       |                     |  |  |  |  |  |

| 30                               | ⊕⊕                     |                                                                                          |                                                                                                                        |           |                       |                     |  |  |  |  |  |

| 32<br>33<br>34<br>35             | CTLP Amp               | Open gain  No oscillation during all feedback  Output D range 0 to                       | to 5V                                                                                                                  | (no load) | 10kHZ<br>nodB<br>nin. |                     |  |  |  |  |  |

|                                  |                        | Output impedance                                                                         | = 2k                                                                                                                   | Ω max.    |                       |                     |  |  |  |  |  |

| 36                               | CTLP IN                | Approximately 2.5V                                                                       | Schmitt input V <sub>TH</sub> 3-level switching<br>Approximately 2.5V internal bias<br>See CTL Schmitt V <sub>TH</sub> |           |                       |                     |  |  |  |  |  |

| 37                               | CFG IN                 | Schmitt input V <sub>TH</sub> approximately ±25m<br>Approximately 2.5V                   |                                                                                                                        | nal _     | Bias                  |                     |  |  |  |  |  |

| Pin<br>No. | Pin Name                                   | Function                                 |                                    |                  |     |                |    |                                       | I/O Format       |

|------------|--------------------------------------------|------------------------------------------|------------------------------------|------------------|-----|----------------|----|---------------------------------------|------------------|

| 39         | CTL CLK                                    | 2-value output, pull u                   | 2-value output, pull up            |                  |     |                |    |                                       |                  |

| 40         | Duty I/O                                   | 2-value input/output, pull up            | pull up Duty Mode VISS mode        |                  |     |                |    |                                       | V <sub>CC</sub>  |

|            |                                            | functions                                |                                    |                  |     |                |    | VISS non-detect                       |                  |

|            |                                            | VI33, VA33                               | VISS, VASS  L Duty = "1" VISS dete |                  |     |                |    | VISS detect (latch)                   |                  |

| 41         | WRITE                                      | 2-value output, pull u<br>See VISS, VASS | р                                  |                  |     | Н              |    | PB CTL, rewrite                       | <sub>↑</sub> Vcc |

|            |                                            |                                          | L Normal                           |                  |     |                |    |                                       |                  |

| 42<br>43   | f <sub>sc</sub> in<br>3f <sub>sc</sub> out |                                          | 50n<br>n                           | n V <sub>p</sub> | p m | in. (<br>in. ( | 31 | f <sub>sc</sub> )                     | € = 10kΩ         |

| 44         | REF 30                                     | See Time Chart.                          |                                    |                  |     |                |    |                                       |                  |

| 45         | Audio-FF                                   | See Head SW Timing                       | J.                                 |                  |     |                |    | · · · · · · · · · · · · · · · · · · · |                  |

| 46         | Video-FF                                   | See Head SW Timing                       | <b>]</b> .                         |                  |     |                |    |                                       |                  |

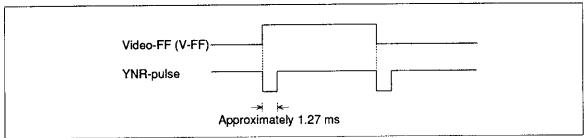

| 47         | YNR-pulse                                  | See On-chip Function                     | ıs.                                |                  |     |                |    |                                       |                  |

| 49         | Mode E                                     | See On-chip Function                     | See On-chip Functions.             |                  |     |                |    |                                       |                  |

| 48         | V-pulse (VP)                               | See On-chip Function                     | ns.                                |                  |     |                |    |                                       | = 20kΩ<br>= 20kΩ |

| Pin<br>No. | Pin Name           | Function                                                                        |                                                      |                         | I/O Format          |  |  |  |

|------------|--------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-------------------------|---------------------|--|--|--|

| 50         | COMP SYNC          | 2-value input. Digital leve<br>capacitive coupling input.                       | l input                                              | or analog               | Input impedance 28Ω |  |  |  |

| 51         | NTSC/PAL/<br>SECAM | 3-value input<br>Open = "M"                                                     |                                                      | Mode                    |                     |  |  |  |

|            | oeo, an            | See External Synchronization                                                    | Н                                                    | NTSC                    |                     |  |  |  |

|            |                    | Synchionization                                                                 | М                                                    | PAL                     |                     |  |  |  |

|            |                    |                                                                                 | ≅ 30kΩ                                               |                         |                     |  |  |  |

| 52         | Power ON<br>Reset  | At power ON, reset perform not flow to CTL head. Be subetween this pin and GND. |                                                      |                         | Vcc<br>≅ 40kΩ       |  |  |  |

| 53         | Serial Data        | 2-value input (Schmitt)                                                         |                                                      |                         | ↑ Vcc               |  |  |  |

| 54         | Serial CLK         | See On-chip Functions.                                                          |                                                      |                         | ≸ ≅ 10kΩ            |  |  |  |

| 55         | CFG C/D            | CFG counts down search sp                                                       | eed c                                                | only and then is output | 2                   |  |  |  |

| 56         | CTL C/D            | CTL counts down search sp                                                       | CTL counts down search speed only and then is output |                         |                     |  |  |  |

| 8<br>31    | GND                | Ground                                                                          | Ground                                               |                         |                     |  |  |  |

| 28<br>38   | V <sub>CC</sub>    | Connected to V <sub>CC</sub> supply                                             |                                                      |                         |                     |  |  |  |

### **Mask ROM Options**

The mask ROM options available with the HD49741NT/HD49733NT are listed below. When ordering mask ROM options, fill in the necessary information in Appendix C Hitachi C-MOS Servo IC ROM Change Specifications, and consult with your Hitachi representative.

The first step is to select the base chip. Appendix A describes the differences between HD49741 and HD49733.

Once a selection is made between HD49741 and HD49733, select from among the five mask ROMs listed below. Generally, the selection of mask ROM options must be based on the mechanical configuration and heads used in the VCR.

#### CFG frequency

Defines the oscillation frequency of the capstan

frequency generator (CFG). Condition: NTSC SP mode frequency

#### **DFG** frequency

Defines the oscillation frequency of the head drum frequency generator (DFG).

Condition: NTSC normal record/playback mode frequency

#### Search speed

Uses integer to set up to 14 search speeds for each record mode.

#### Head angle

Allows setting of up to six switching pulse signal angles for each of the heads: video head, audio head, extra head.

#### VP output polarity

Selects from among three VP signal pulse polarities.

### **Timing Charts**

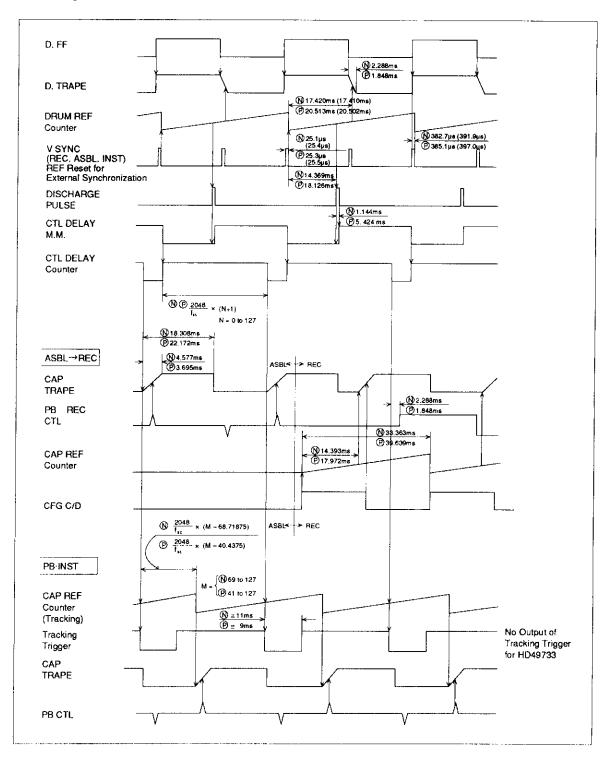

#### **Control Timing Chart**

Values in parentheses are for HD49733NT. N = NTSC/P = PAL

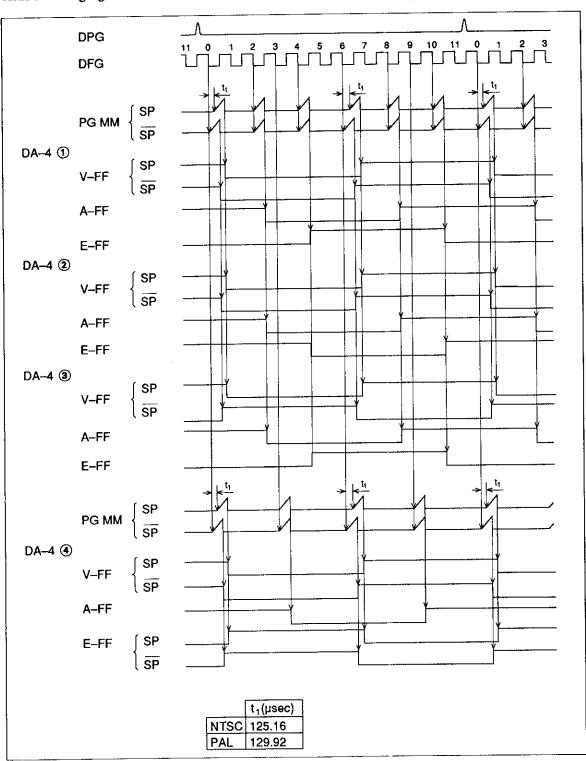

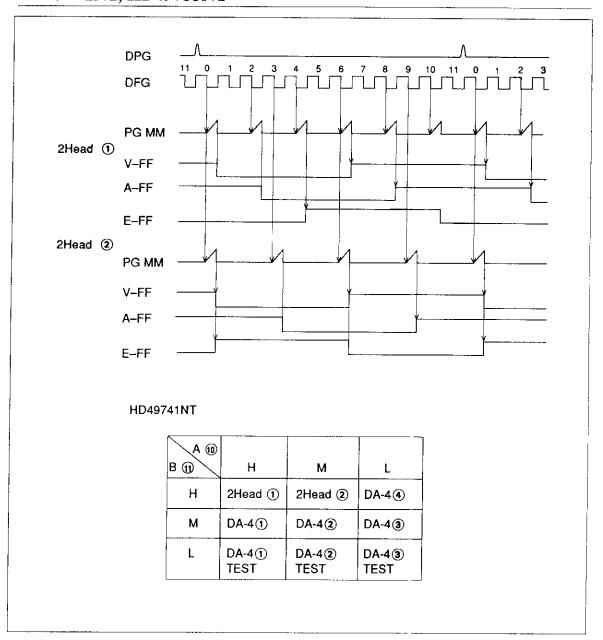

## Head Switching System Control Timing Chart (HD49741NT)

SP = LP or EP mode Head switching signal

## Absolute Maximum Ratings (Ta = 25°C)

| Item                     | Symbol           | HD49733NT  | HD49741NT  | Unit |

|--------------------------|------------------|------------|------------|------|

| Supply voltage           | V <sub>DD</sub>  | 7.0        | 7.0        | V    |

| Operating supply voltage | V <sub>opr</sub> | 4.5 to 6.0 | 4.5 to 6.0 | V    |

| Storage temperature      | T <sub>stg</sub> | -40 to 125 | -40 to 125 | °C   |

| Operating temperature    | T <sub>opr</sub> | -10 to 70  | -10 to 70  | °C   |

| Power dissipation        | P <sub>T</sub>   | 500        | 500        | mW   |

## Electrical Characteristics ( $V_{CC} = 5V$ , $Ta = 25^{\circ}C$ )

| N  | Test<br>o. Item                               | Symbol           | Min  | Тур  | Max  | Unit | Test Condition                               | Applicable<br>Pin                          | Test<br>Circuit                       | Note |

|----|-----------------------------------------------|------------------|------|------|------|------|----------------------------------------------|--------------------------------------------|---------------------------------------|------|

| 1  | Supply current                                | lcc              | 8.0  | 20.0 | 32.0 | mA   | Quiescent<br>Pins 28 and 38 total            | 28, 38                                     |                                       |      |

| 2  | 2-value output<br>voltage                     | V <sub>OL</sub>  |      | 0.0  | 0.05 | ٧    | Quiescent                                    | 1 to 4, 44 to 47<br>49, 55, 56             |                                       |      |

| 3  | Same as above                                 | V <sub>OH</sub>  | 4.9  | 5.0  | _    | ٧    | Quiescent                                    | Same as above                              |                                       |      |

| 4  | Same as above                                 | V <sub>IL</sub>  |      | 0.6  | 1.2  | ٧    | Load current = 2mA                           | Same as above                              |                                       |      |

| 5  | Same as above                                 | V <sub>IH</sub>  | 3.8  | 4.4  |      | ٧    | Load current = 2mA                           | Same as above                              |                                       |      |

| 6  | Pull up output<br>voltage                     | V <sub>OL</sub>  | 0.0  | 0.1  | 0.3  | ٧    | No load                                      | 39, 40                                     |                                       |      |

| 7  | Same as above                                 | V <sub>OH</sub>  | 4.9  | 5.0  |      | ٧    | No load                                      | 39, 40                                     |                                       |      |

| 8  | Same as above                                 | V <sub>IL</sub>  | _    | 0.6  | 1.2  | V    | Load current = 2mA                           | 39, 40                                     |                                       |      |

| 9  | Pull up resistance                            | R <sub>H</sub>   | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 39, 40                                     |                                       |      |

| 10 | 3-value output<br>voltage                     | V <sub>OL</sub>  | 0.0  | 0.2  | 0,4  | V    | No load                                      | 48                                         |                                       |      |

| 11 | Same as above                                 | V <sub>OM</sub>  | 2.3  | 2.5  | 2.8  | ٧    | No load                                      | 48                                         |                                       |      |

| 12 | Same as above                                 | V <sub>OL</sub>  | 4.6  | 4.8  | 5.0  | ٧    | No load                                      | 48                                         | · · · · · · · · · · · · · · · · · · · |      |

| 13 | Same as above                                 | V <sub>IL</sub>  |      | 0.6  | 1.2  | ٧    | Load current = 1mA                           | 48                                         |                                       |      |

| 14 | Same as above                                 | V <sub>IH</sub>  | 3.8  | 4.4  | _    | ٧    | Load current = 1mA                           | 48                                         |                                       |      |

| 15 | 3-value output<br>M level output<br>impedance | R <sub>M</sub>   | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 48                                         |                                       |      |

| 16 | REC CTL output<br>pin-to-pin voltage          | V <sub>CTL</sub> | 4.4  | 4.6  | 4.8  | V    | No load<br>Voltage between pins<br>29 and 30 | 29, 30                                     |                                       |      |

| 17 | REC CTL output impedance                      | R <sub>CTL</sub> | 300  | 500  | 1000 | Ω    | I < 3mA<br>Pins 29 and 30 total              | 29, 30                                     |                                       |      |

| 18 | 2-value input V <sub>TH</sub>                 | V <sub>TH</sub>  | 1.5  | 2.5  | 3.5  | V    |                                              | 19, 40, 41, 53, 54<br>(40, 41, 52, 53, 54) |                                       |      |

| 19 | 2-value input pull<br>up resistance 1         | R <sub>HI</sub>  | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 40, 41, 53, 54                             |                                       |      |

| 20 | 2-value input pull<br>up resistance 2         | R <sub>H2</sub>  | 24.0 | 36.0 | 52.0 | kΩ   |                                              | 19 (52)                                    |                                       | •    |

## Electrical Characteristics ( $V_{CC} = 5V$ , Ta = 25°C) (cont)

| No. | Test<br>Item                           | Symbol            | Min  | Тур  | Max  | Unit             | Test Condition      | Applicable<br>Pin                      | Test<br>Circuit | Note |

|-----|----------------------------------------|-------------------|------|------|------|------------------|---------------------|----------------------------------------|-----------------|------|

| 21  | 3-value input V <sub>TH</sub>          | V <sub>TH1</sub>  | 1.0  | 1.4  | 1.9  | ٧                | L/M V <sub>TH</sub> | (9 to 11, 19, 15)<br>10, 11, 51        |                 |      |

| 22  | 3-value input V <sub>TH</sub>          | V <sub>TH2</sub>  | 3.1  | 3.5  | 4.0  | ٧                | M/H V <sub>TH</sub> | Same as above                          |                 |      |

| 23  | 3-value input pin voltage              | V <sub>M</sub>    | 2.0  | 2.5  | 2.9  | ٧                |                     | Same as above                          |                 |      |

| 24  | 3-value input resistance               | R <sub>M1</sub>   | 18.5 | 28.0 | 42.0 | kΩ               |                     | Same as above<br>(10, 11, 19, 51)      |                 |      |

| 25  | 3-f <sub>sc</sub> input<br>sensitivity | V <sub>3fsc</sub> |      | _    | 350  | mV <sub>pp</sub> |                     | 42                                     |                 |      |

| 26  | f <sub>sc</sub> input sensitivity      | V <sub>fsc</sub>  | _    | _    | 150  | mV <sub>pp</sub> |                     | 42                                     |                 |      |

| 27  | Schmitt input<br>pin voltage 1         | V <sub>IS1</sub>  | 2.2  | 2.5  | 2.8  | ٧                |                     | 36                                     |                 |      |

| 28  | CTLP Schmitt input V <sub>TH</sub>     | V <sub>+TH1</sub> | 100  | 130  | 160  | mV <sub>p</sub>  | Normal speed        | 36                                     |                 |      |

| 29  | Same as above                          | V <sub>-TH1</sub> | -160 | -130 | -100 | mV <sub>p</sub>  | Normal speed        | 36                                     |                 |      |

| 30  | Same as above                          | V <sub>+TH2</sub> | 200  | 260  | 320  | mV <sub>p</sub>  | Mid-speed search    | 36                                     |                 |      |

| 31  | Same as above                          | V <sub>-TH2</sub> | -320 | -260 | -200 | mV <sub>p</sub>  | Mid-speed search    | 36                                     | <u>,</u>        |      |

| 32  | Same as above                          | V <sub>+TH3</sub> | 420  | 500  | 580  | $mV_p$           | High-speed search   | 36                                     |                 |      |

| 33  | Same as above                          | V_TH3             | -580 | -500 | -420 | mV <sub>p</sub>  | High-speed search   | 36                                     |                 |      |

| 34  | Schmitt input pin voltage 2            | V <sub>IS2</sub>  | 2.3  | 2.7  | 3.1  | ٧                |                     | 9, 37                                  |                 |      |

| 35  | FG Schmitt<br>input V <sub>TH</sub>    | V <sub>+TH</sub>  | 100  | 250  | 400  | mV <sub>p</sub>  |                     | 9, 37                                  |                 |      |

| 36  | Same as above                          | V <sub>-TH</sub>  | -30  | 0    | 30   | mV <sub>p</sub>  |                     | 9, 37                                  |                 |      |

| 37  | Schmitt input pin voltage 3            | V <sub>IS3</sub>  | 1.8  | 2.2  | 2.6  | V                |                     | 7                                      |                 |      |

| 38  | PG Schmitt input V <sub>TH</sub>       | V <sub>+TH</sub>  | 0.5  | 8.0  | 1.1  | ٧                |                     | 7                                      |                 |      |

| 39  | Same as above                          | V <sub>-TH</sub>  | 0.2  | 0.4  | 0.6  | ٧                |                     | 7                                      |                 |      |

| 40  | Analog SW<br>ON-state resistance       | R <sub>ASW</sub>  | 150  | 300  | 500  | Ω                |                     | 15 to 18, 22 to 2<br>29, 30, 32, 34, 3 |                 |      |

## Electrical Characteristics ( $V_{CC} = 5V$ , $Ta = 25^{\circ}C$ ) (cont)

| No | Test<br>. Item                       | Symbol            | Min  | Тур  | Max  | Unit            | Test Condition                                       | Applicable<br>Pin | Test<br>Circuit                        | Note |

|----|--------------------------------------|-------------------|------|------|------|-----------------|------------------------------------------------------|-------------------|----------------------------------------|------|

| 41 | Power on reset input V <sub>TH</sub> | V <sub>52TH</sub> | 2.9  | 3.5  | 4.1  | ٧               |                                                      | 52                |                                        |      |

| 42 | Power on reset pull up resistance    | R <sub>52</sub>   | 24.0 | 36.0 | 52.0 | kΩ              |                                                      | 52                |                                        |      |

| 43 | Sync input V <sub>TH</sub>           | V <sub>50TH</sub> | 1.5  | 2.5  | 3.5  | ٧               | DC input                                             | 50                |                                        |      |

| 44 | Sync input pin voltage               | V <sub>50</sub>   | 1.8  | 2.4  | 3.0  | ٧               |                                                      | 50                | 1,4                                    |      |

| 45 | Sync input sensitivity               | V <sub>SYC</sub>  | 90   | 140  | 190  | mV <sub>p</sub> | Peak value from pin voltage for capacitive coupling. | 50                | ************************************** |      |

| 46 | Sync input impedance                 | R <sub>50</sub>   | 18.5 | 28.0 | 42.0 | kΩ              |                                                      | 50                |                                        |      |

| 47 | Mono-multi V <sub>TH</sub>           |                   |      | 2.5  |      | V               | Each mono/multi V <sub>TH</sub>                      | 5,6               |                                        |      |

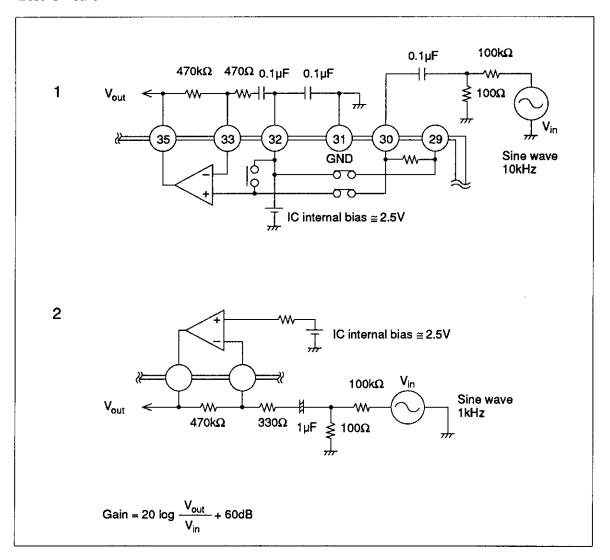

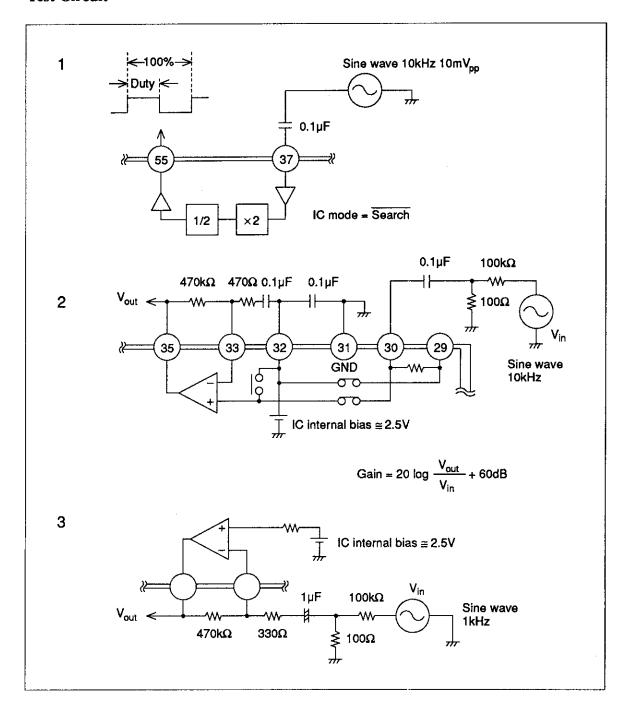

| 48 | CTLP Amp Gain                        | A <sub>CTL</sub>  | 57   | 60   | 62   | dB              | f = 10kHz                                            |                   | 1                                      |      |

| 49 | CTLP Amp Gain                        | A <sub>CILO</sub> |      | 85   | _    | dB              | Open loop gain                                       |                   | <u> </u>                               |      |

|    | DRUM ADD<br>Amp Gain                 | A <sub>D</sub>    | 57   | 60   | 62   | ďВ              | f = 1kHz                                             |                   | 2                                      |      |

| 51 | Same as above                        | A <sub>D0</sub>   | ***  | 85   | _    | dB              | Open loop gain                                       |                   |                                        |      |

|    | CAPSTAN ADD<br>Amp Gain              | Ac                | 57   | 60   | 62   | dB              | f = 1kHz                                             |                   | 2                                      |      |

| 53 | Same as above                        | A <sub>C0</sub>   | -    | 85   |      | dB              | Open loop gain                                       | P-11              | <u>-</u>                               |      |

### **Test Circuit**

## Electrical Characteristics ( $V_{CC} = 5V$ , $Ta = 25^{\circ}C$ ) (HD49733)

| No | Test<br>. Item                                | Symbol           | Min  | Тур  | Max  | Unit | Test Condition                               | Applicable<br>Pin              | Test<br>Circuit | Note |

|----|-----------------------------------------------|------------------|------|------|------|------|----------------------------------------------|--------------------------------|-----------------|------|

| 1  | Supply current                                | Icc              | 8.0  | 20.0 | 32.0 | mA   | No load<br>Pins 28 and 38 total              | 28, 38                         |                 |      |

| 2  | 2-value output<br>voltage                     | V <sub>OL</sub>  | _    | 0.0  | 0.05 | V    | No load                                      | 1 to 4, 44 to 47<br>49, 55, 56 |                 |      |

| 3  | Same as above                                 | V <sub>OH</sub>  | 4.9  | 5.0  | _    | ٧    | No load                                      | Same as above                  |                 |      |

| 4  | Same as above                                 | V <sub>IL</sub>  | _    | 0.6  | 1.2  | ٧    | Load current = 2mA                           | Same as above                  |                 |      |

| 5  | Same as above                                 | V <sub>IH</sub>  | 3.8  | 4.4  |      | ٧    | Load current = 2mA                           | Same as above                  |                 |      |

| 6  | Pull up output<br>voltage                     | V <sub>OL</sub>  | 0.0  | 0.1  | 0.3  | ٧    | No load                                      | 39, 40                         |                 |      |

| 7  | Same as above                                 | V <sub>OH</sub>  | 4.9  | 5.0  |      | V    | No load                                      | 39, 40                         |                 |      |

| 8  | Same as above                                 | V <sub>IL</sub>  | _    | 0.6  | 1.2  | V    | Load current = 2mA                           | 39, 40                         |                 | -    |

| 9  | Pull up resistance                            | R <sub>H</sub>   | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 39, 40                         |                 |      |

| 10 | 3-value output voltage                        | V <sub>OL</sub>  | 0.0  | 0.2  | 0.4  | ٧    | No load                                      | 48                             |                 |      |

| 11 | Same as above                                 | V <sub>OM</sub>  | 2.3  | 2.5  | 2.8  | V    | No load                                      | 48                             |                 |      |

| 12 | Same as above                                 | V <sub>OH</sub>  | 4.6  | 4.8  | 5.0  | ٧    | No load                                      | 48                             |                 |      |

| 13 | Same as above                                 | V <sub>IL</sub>  | -    | 0.6  | 1.2  | V    | Load current = 1mA                           | 48                             |                 |      |

| 14 | Same as above                                 | V <sub>IH</sub>  | 3.8  | 4.4  | _    | ٧    | Load current = 1mA                           | 48                             |                 |      |

| 15 | 3-value output<br>M level output<br>impedance | R <sub>M</sub>   | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 48                             |                 |      |

| 16 | REC CTL output<br>pin-to-pin voltage          | V <sub>CTL</sub> | 4.4  | 4.6  | 4.8  | V    | No load<br>Voltage between pins<br>29 and 30 | 29, 30                         |                 |      |

| 17 | REC CTL output impedance                      | R <sub>CTL</sub> | 300  | 550  | 1000 | Ω    | I < 3mA<br>Pins 29 and 30 total              | 29, 30                         |                 |      |

| 18 | 2-value input V <sub>TH</sub>                 | V <sub>TH</sub>  | 1.5  | 2.5  | 3.5  | V    |                                              | 40, 41, 52, 53, 54             | 4               |      |

| 19 | 2-value input pull<br>up resistance 1         | R <sub>H1</sub>  | 6.0  | 9.0  | 13.0 | kΩ   |                                              | 40, 41, 53, 54                 |                 |      |

| 20 | 2-value input<br>pull up resistance 2         | R <sub>H2</sub>  | 24.0 | 36.0 | 52.0 | kΩ   |                                              | 52                             |                 |      |

## Electrical Characteristics ( $V_{CC} = 5V$ , $Ta = 25^{\circ}C$ ) (HD49733)

| No. | Test<br>Item                           | Symbol            | Min  | Тур  | Max  | Unit             | Test Condition      | Applicable<br>Pin                      | Test<br>Circuit | Note |

|-----|----------------------------------------|-------------------|------|------|------|------------------|---------------------|----------------------------------------|-----------------|------|

| 21  | 3-value input V <sub>TH</sub>          | V <sub>TH1</sub>  | 1.0  | 1.4  | 1,9  | ٧                | L/M V <sub>TH</sub> | 9 to 11, 19, 51                        |                 |      |

| 22  | 3-value input V <sub>TH</sub>          | V <sub>TH2</sub>  | 3.1  | 3.5  | 4.0  | ν                | M/H V <sub>TH</sub> | 9 to 11, 19, 51                        |                 |      |

| 23  | 3-value input<br>pin voltage           | V <sub>M</sub>    | 2.0  | 2.5  | 2.9  | ٧                |                     | 9 to 11, 19, 51                        |                 |      |

| 24  | 3-value input resistance 1             | R <sub>M1</sub>   | 18.5 | 28.0 | 42.0 | kΩ               |                     | 10, 11, 19, 51                         |                 |      |

| 25  | 3-value input resistance 2             | R <sub>M2</sub>   | 6.5  | 9.4  | 13.5 | kΩ               |                     | 9                                      |                 |      |

| 26  | 3-f <sub>sc</sub> input<br>sensitivity | V <sub>3fsc</sub> | _    | _    | 350  | mV <sub>pp</sub> |                     | 42                                     |                 |      |

| 27  | f <sub>sc</sub> input sensitivity      | V <sub>fsc</sub>  | _    |      | 150  | mV <sub>pp</sub> |                     | 42                                     |                 |      |

| 28  | Schmitt input pin voltage              | V <sub>IS</sub>   | 2.2  | 2.5  | 2.8  | ٧                |                     | 36, 37                                 |                 |      |

| 29  | CTLP Schmitt input V <sub>TH</sub>     | V <sub>+TH1</sub> | 100  | 130  | 160  | mV <sub>p</sub>  | Normal speed        | 36                                     |                 |      |

| 30  | Same as above                          | V <sub>-TH1</sub> | 100  | 130  | 160  | mV <sub>p</sub>  | Normal speed        | 36                                     |                 |      |

| 31  | Same as above                          | V <sub>+TH2</sub> | 200  | 260  | 320  | mV <sub>ρ</sub>  | Mid-speed search    | 36                                     |                 |      |

| 32  | Same as above                          | V <sub>-TH2</sub> | 200  | 260  | 320  | mV <sub>p</sub>  | Mid-speed search    | 36                                     |                 |      |

| 33  | Same as above                          | V <sub>+TH3</sub> | 420  | 500  | 580  | mV <sub>p</sub>  | High-speed search   | 36                                     |                 |      |

| 34  | Same as above                          | V_ <sub>TH3</sub> | 420  | 500  | 580  | $mV_p$           | High-speed search   | 36                                     |                 |      |

| 35  | CFG Schmitt input duty ratio           | DR                | 45   | 50   | 55   | %                |                     | 37                                     | 1               |      |

| 36  | Analog SW<br>ON-state resistance       | R <sub>ASW</sub>  | 150  | 300  | 500  | Ω                |                     | 15 to 18, 22 to 2<br>29, 30, 32, 34, 3 |                 |      |

| 37  | CTLP Amp Gain                          | A <sub>CTL</sub>  | 57.0 | 60.0 | 62.0 | dB               | f = 10kHz           |                                        | 2               |      |

| 38  | CTLP Amp Gain                          | A <sub>CTLO</sub> | _    | 85   | _    | dB               | Open loop gain      |                                        |                 |      |

| 39  | DRUM ADD<br>Amp Gain                   | A <sub>D</sub>    | 57.0 | 60.0 | 62.0 | dB               | f = 1kHz            |                                        | 3               |      |

| 40  | Same as above                          | A <sub>DO</sub>   |      | 85   | _    | dB               | Open loop gain      |                                        |                 |      |

## Electrical Characteristics ( $V_{CC} = 5V$ , $Ta = 25^{\circ}C$ ) (HD49733)

| No | Test<br>. Item                               | Symbol            | Min  | Тур  | Max  | Unit | Test Condition                  | Applicable<br>Pin | Test<br>Circuit | Note        |

|----|----------------------------------------------|-------------------|------|------|------|------|---------------------------------|-------------------|-----------------|-------------|

| 41 | CAPSTAN ADD<br>Amp Gain                      | A <sub>C</sub>    | 57.0 | 60.0 | 62.0 | dB   | f = 1kHz                        |                   | 3               |             |

| 42 | Same as above                                | A <sub>CO</sub>   |      | 85   | _    | dB   | Open loop gain                  | -                 |                 |             |

| 43 | Pin 50 DC<br>input V <sub>TH</sub>           | V <sub>TH50</sub> | 1.8  | 2.5  | 3.0  | ٧    |                                 | 50                |                 | <del></del> |

| 44 | Pin 50 bias<br>potential                     | V <sub>50</sub>   | 0.5  | 1.0  | 1.5  | V    |                                 | 50                |                 |             |

| 45 | Pin 50 capacitive coupling input sensitivity | V <sub>SYNC</sub> | _    | 1.5  | 2.5  | Vp   |                                 | 50                |                 |             |

| 46 | Pin 50 input resistance                      | R <sub>50</sub>   | 20   | 43   | 80   | kΩ   |                                 | 50                |                 |             |

| 47 | Mono-multi V <sub>TH</sub>                   |                   |      | 2.5  |      | ٧    | Each mono-multi V <sub>TH</sub> | 1                 |                 |             |

|    | Pin 6 applied voltage                        | V <sub>6</sub>    |      | _    | 3.1  | ٧    | Approved applied vol            | tage              |                 |             |

### **Test Circuit**

# Appendix A — Comparison of HD49741 and HD49733

#### General

HD49741 and HD49733 are Hitachi CMOS servo LSI base chips. Though their functions are basically the same, these two chips have some differences. Note that even for functions that are the same for both chips, their pin numbering differs, as do their mode pins and functions.

The following are the main differences between the two chips:

- HD49741 has two individual pins for PG and DFG input, while HD49733 has one pin

- HD49733 has a on-chip doubler for CFG input, and CFG frequency can be set in the range of 360 to 1440Hz

Both HD49741 and HD49733 are available in the DP-56S package.

The following chart shows the functional differences between HD49741 and HD49733. Chip selection should be made based on the motor requirements of the system.

|    | ltem                                   | HD49741                     | HD49733                                                  | See<br>paragraph |

|----|----------------------------------------|-----------------------------|----------------------------------------------------------|------------------|

| 1  | PG, DFG input                          | One pin each (2 pins total) | One pin, combined input                                  | 1                |

| 2  | CFG input                              | Detection at fall only      | Detection at rise and fall (on-chip doubler)             | 2                |

| 3  | Extra-FF output                        | Yes                         | No                                                       |                  |

| 4  | Ex-reset                               | Special pin (Pin 51)        | Input along with C-sync input (Pin 50)                   | 3                |

| 5  | TR TRG<br>(tracking trigger<br>output) | Yes                         | No                                                       | _                |

| 6  | Supplemental<br>V output               | 2 pins (Pins 48, 49)        | 1 pin (Pin 48)                                           | 4                |

| 7  | YNR output                             | No                          | Yes                                                      | 5                |

| 8  | Frame shift                            | No                          | Yes                                                      | 6                |

| 9  | Mode output                            | ABCDE                       | A, B, C, D, E(CFG C/D out<br>CTLP C/D out)               | 7                |

| 10 | Supplemental<br>V delay shift          | Serial control              | Externally added 6H fixed CR mono-multi and combinations | 8                |

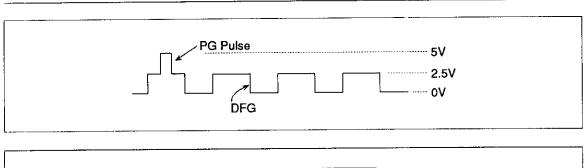

### PG, DFG input